# Make Life Easier for Embedded Software Engineers Facing Complex Hardware Architectures

R. Leconte, E. Jenn, G. Bois, H. Guérard IRT Saint Exupéry, Space Codesign, Thales AVS

### AGENDA

- SpaceStudio and deployment to hybrid HW/SW platform

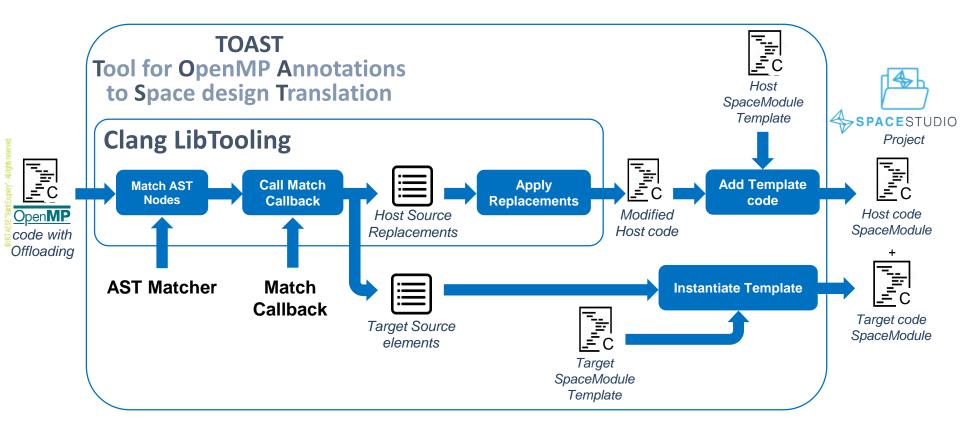

- TOAST (Tool for OpenMP Annotations to Space design Translation) and its purpose

- OpenMP Offloading

- Example on a LineDetection algorithm

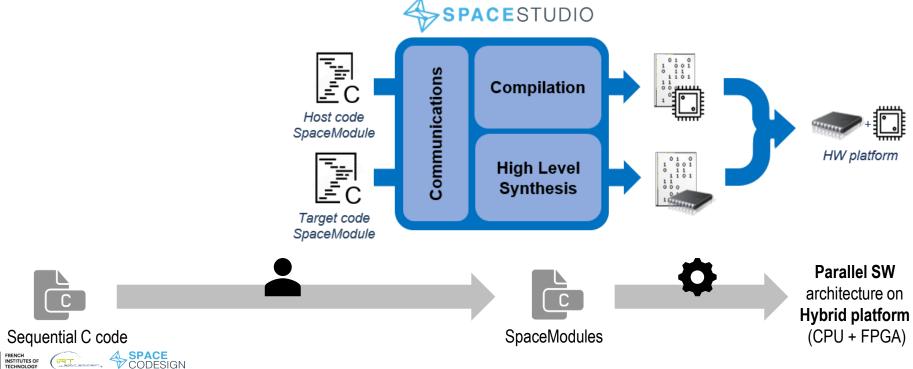

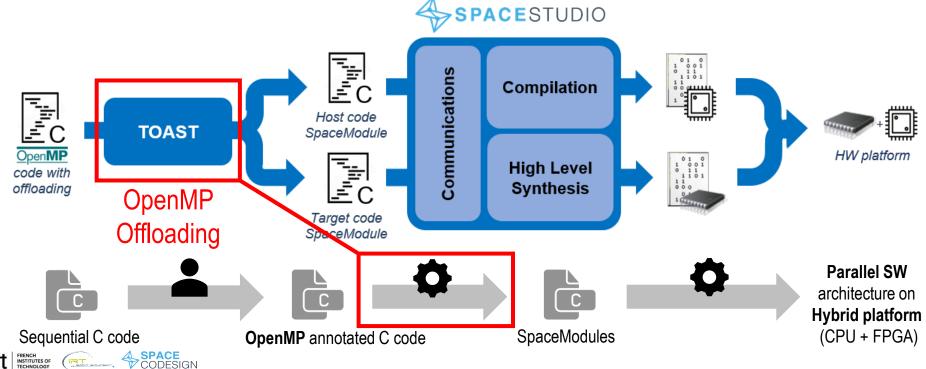

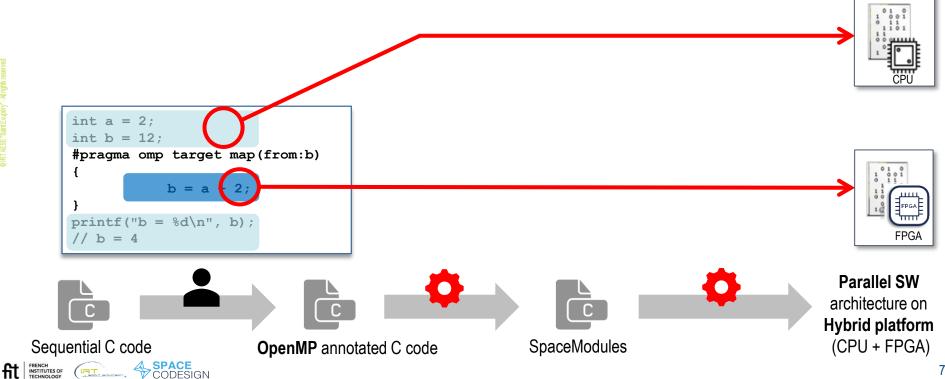

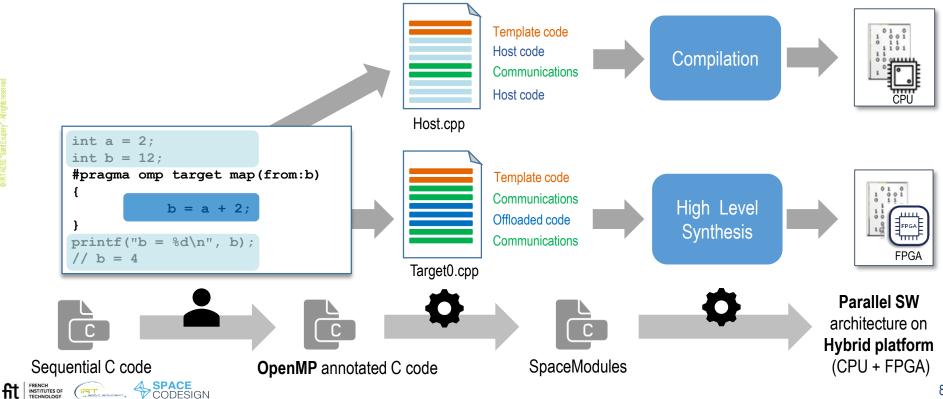

- Workflow based on an existing tool: SpaceStudio to expose parallelism

- Encapsulate logic inside **SpaceModules**

fit

- Use **OpenMP** to **expose parallelism**

- Then TOAST generates SpaceModules

- Finally SpaceStudio deploys to the target platform

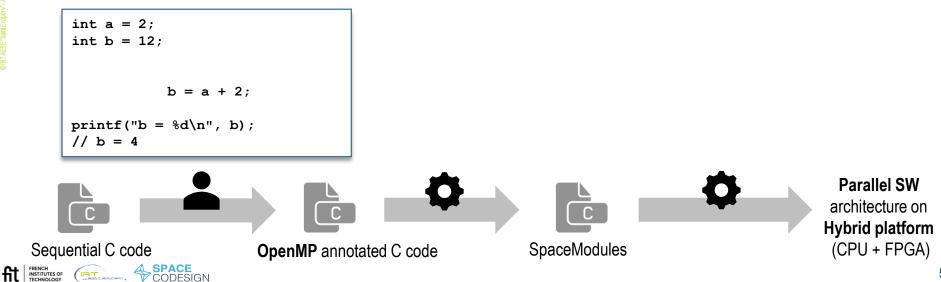

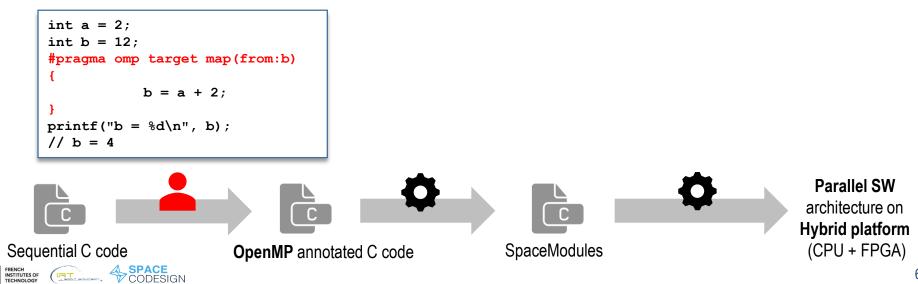

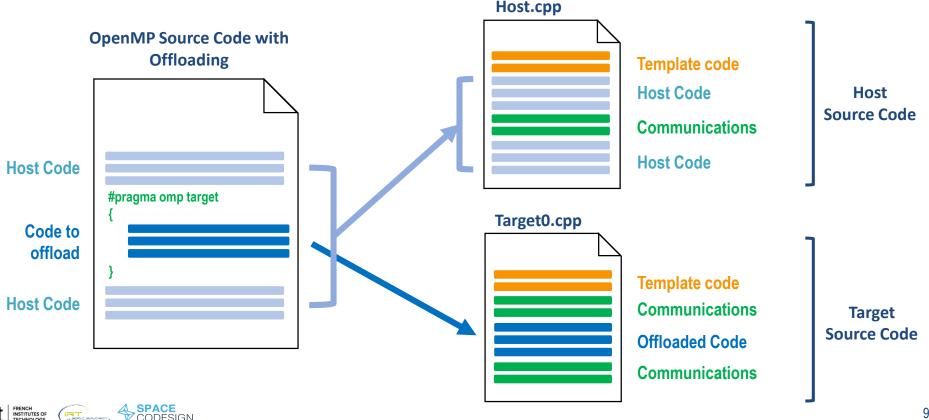

OpenMP allows to offload computations to an accelerator:

GPU, FPGA, etc.

OpenMP allows to offload computations to an accelerator • GPU, FPGA, etc.

fit

OpenMP allows to offload computations to an accelerator • GPU, FPGA, etc.

OpenMP allows to offload computations to an accelerator

## • **TOAST converts** OpenMP annotated code into C/C++ code using SpaceStudio Communication APIs

TECHNOLOGY

### **TOAST Architecture**

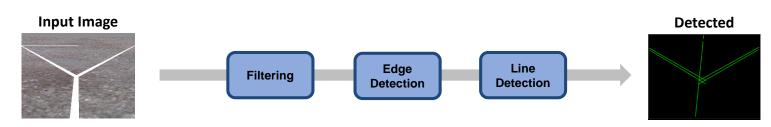

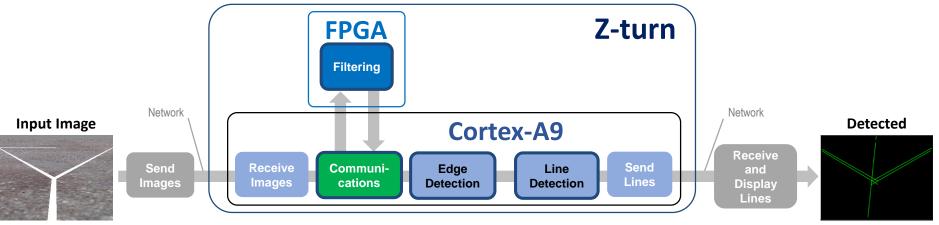

### **LineDetection Use Case**

#### Line Detection and test bench

french INSTITUTES OF TECHNOLOGY SPACE CODESIGN

IRT CHURCH

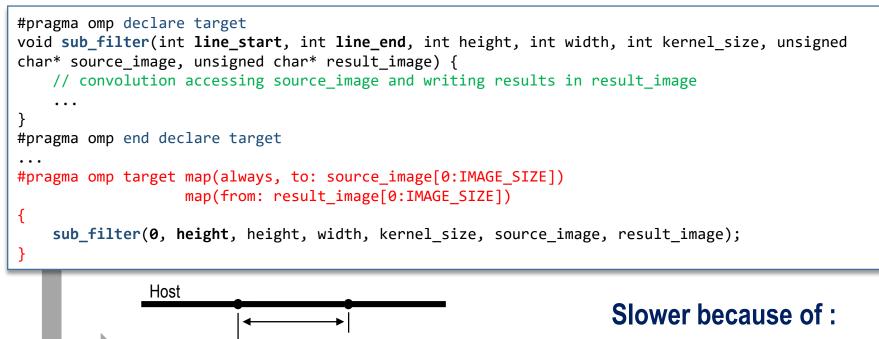

### **LineDetection: One Accelerator**

Accelerator

Convolution

Host

Communications

- Communications

- Low FPGA frequency

FRENCH INSTITUTES OF

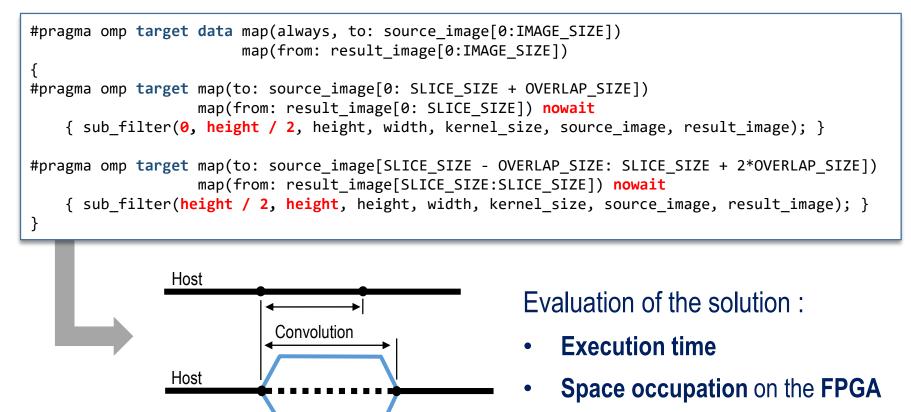

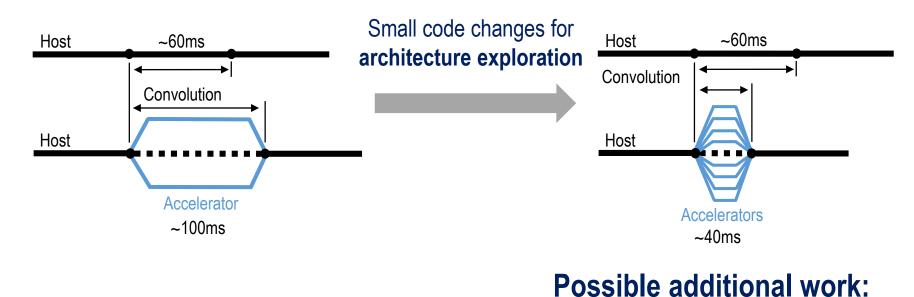

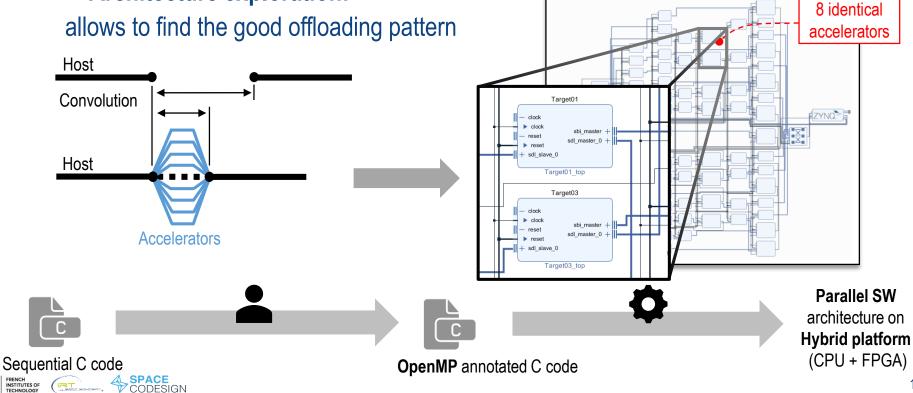

### **LineDetection : Several Accelerators**

```

#pragma omp target map(always, to: source_image[0:IMAGE_SIZE])

map(from: result image[0:IMAGE SIZE])

{

sub filter(0, height, height, width, kernel size, source image, result image);

}

#pragma omp target data map(always, to: source_image[0:IMAGE_SIZE])

map(from: result image[0:IMAGE SIZE])

#pragma omp target map(to: source image[0: SLICE SIZE + OVERLAP SIZE])

map(from: result image[0: SLICE SIZE]) nowait

{ sub filter(0, height / 2, height, width, kernel size, source image, result image); }

#pragma omp target map(to: source_image[SLICE_SIZE - OVERLAP_SIZE: SLICE SIZE + 2*OVERLAP SIZE])

map(from: result image[SLICE SIZE:SLICE SIZE]) nowait

{ sub_filter(height / 2, height, height, width, kernel_size, source image, result image); }

}

```

FRENCH INSTITUTES OF TECHNOLOGY

### **LineDetection : Several Accelerators**

Accelerator

FRENCH INSTITUTES OF

### **LineDetection : Several Accelerators**

HLS pragmas -> ~17ms

15

FRENCH INSTITUTES OF

TECHNOLOGY

SPACE CODESIGN

# OpenMP allows to offload computations to multiple accelerators

• Architecture exploration:

fit

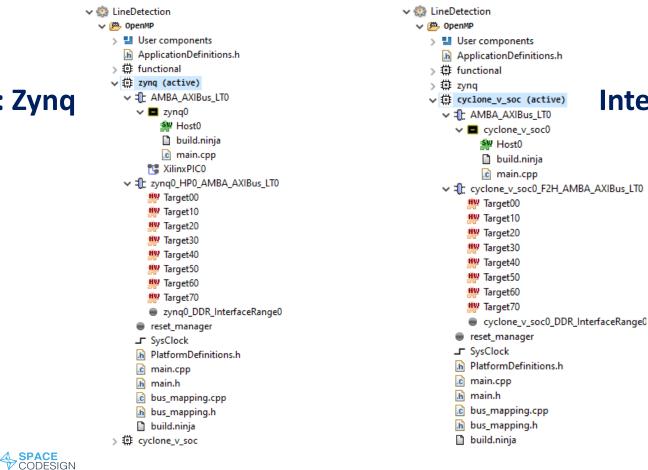

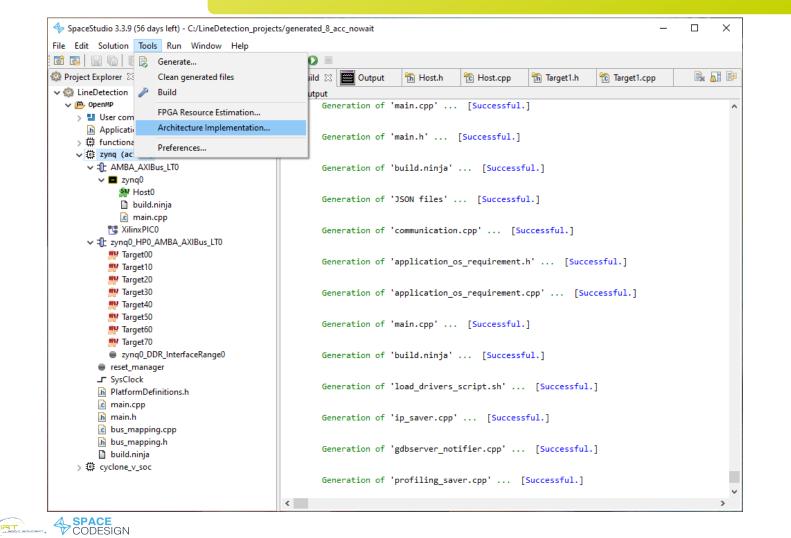

### **Architectures in SpaceStudio**

#### Intel : Cyclone

### Xilinx : Zynq

FRENCH

RT CHUPERY

fit INSTITUTES OF TECHNOLOGY

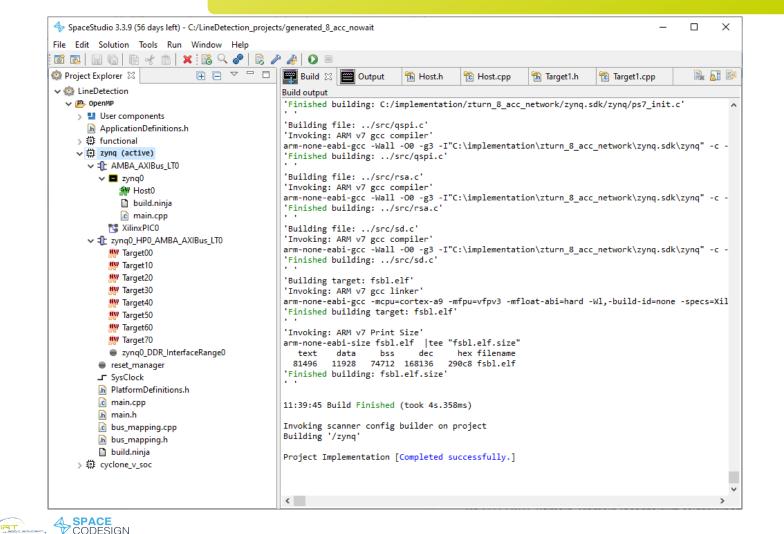

FRENCH INSTITUTES OF TECHNOLOGY 💠 SpaceStudio 3.3.9 (56 days left) - C:/LineDetection\_projects/generated\_8\_acc\_nowait

-  $\Box$   $\times$

File Edit Solution Tools Run Window Help

| ✓ 🕮 OpenMP                          | Generation of 'main.cpp' [Successful.]                          |

|-------------------------------------|-----------------------------------------------------------------|

| > 🛂 User components                 |                                                                 |

| h ApplicationDefinitions.h          | Image: Architecture Implementation export                       |

| > 4 functional                      | Architecture Implementation                                     |

| 〜 弾 zynq (active)                   |                                                                 |

| ✓ =[]; AMBA_AXIBus_LT0              | Implements a complete system on a physical FPGA board           |

| ✓ ■ zynq0<br>೨೫ Host0               |                                                                 |

| build.ninja                         | Project directory: C:/implementation/zturn_8_acc Browse         |

| i main.cpp                          | Electronic Design Automation (EDA) tool: Xilinx - Vivado 2018.3 |

| TS XilinxPIC0                       |                                                                 |

| ✓ ℑ<br>U; zynq0_HP0_AMBA_AXIBus_LT0 | Board: Z-turn 7z020                                             |

| 👭 Target00                          | High-level synthesis: Vivado HLS                                |

| 郷 Target10                          | Modules to synthesize                                           |

| 🏧 Target20                          | inouties to synthesize                                          |

| Target30                            | Module name                                                     |

| III Target40                        | Target00                                                        |

| 👭 Target50<br>👭 Target60            | ☑ Target10                                                      |

| Target70                            | Target20                                                        |

| zynq0_DDR_InterfaceRange0           | ✓ Target30                                                      |

| <pre>reset_manager</pre>            | ✓ Target40                                                      |

|                                     | ☑ Target50                                                      |

| h PlatformDefinitions.h             | ☑ Target60                                                      |

| c main.cpp                          | ☑ Target70                                                      |

| h main.h                            |                                                                 |

| ■ bus_mapping.cpp                   |                                                                 |

| bus_mapping.h build.ninja           | OK Cancel                                                       |

| > # cyclone_v_soc                   | Or Cancer                                                       |

|                                     | Generation of 'profiling saver.cpp' [Successful.]               |

FRENCH INSTITUTES OF TECHNOLOGY

FRENCH

TECHNOLOGY

INSTITUTES OF

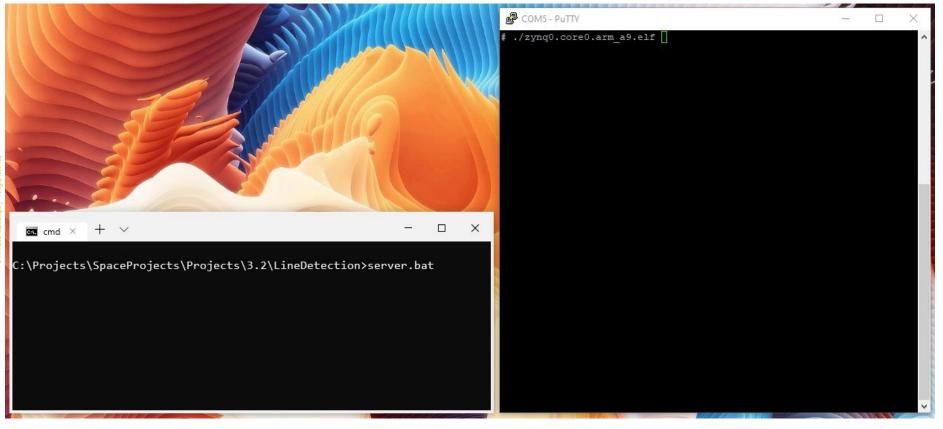

### Video: application running on Z-turn

## Conclusion

# **TOAST** allows to leverage the **OpenMP Offloading** standard to deploy software on **FPGA**s using **SpaceStudio**

• OpenMP is a well established standard

# Our workflows allows:

- Design space exploration

- Deployment on SoCs featuring an FPGA

- Support multiple vendors (Xilinx, Intel)

# Thank you for your attention

© IRT AESE "Saint Exupéry" - All rights reserved. This document and all information contained herein is the sole property of IRT AESE "Saint Exupéry". No intellectual property rights are granted by the delivery of this document or the disclosure of its content. IRT AESE "Saint Exupéry" and its logo are registered trademarks.